With the evolution of high-performance computing in the fields of Artificial Intelligence (AI) and Machine Learning (ML), various applications are demanding unprecedented levels of computational complexity, massive storage capacity, and seamless connectivity. Faster and more efficient communication between electronic components enables purpose-built generative AI data centers to process massive datasets and provide real-time responses in the form of text, video, audio, and images.

To meet performance demands, data center architects must scale system architectures to support 224 Gbps data transfer rates through PAM4 modulation schemes. This presents significant challenges for interconnect solutions, driving the adoption of new technologies while leveraging advanced strategies in routing, spatial efficiency, and power management.

To support these new data center architectures, the industry has introduced a range of comprehensive interconnect solutions, including high-speed board-to-board connectors, next-generation cables, backplanes, and near-ASIC connector-to-cable solutions, operating at speeds of up to 224 Gbps-PAM4.

Approaching the Limits of Physics

Reimagining the 224 Gbps-PAM4 ecosystem's connectivity requires architectural innovation to overcome performance barriers. While 112 Gbps-PAM4 signaling was a significant technological breakthrough, increasing to 224 Gbps offers substantial performance gains, far beyond merely "doubling the bandwidth." Systems designed for 224 Gbps data transfer rates face daunting physical challenges, including signal integrity, reducing electromagnetic interference (EMI), and thermal management.

Another challenge lies in squeezing more capacity and connectivity into ever-shrinking spaces while continuously improving performance. Therefore, it is not merely a matter of upgrading underlying computing and connectivity capabilities to support 224 Gbps rates but rather redesigning AI data centers to optimally leverage 224 Gbps technological innovations. This requires a new level of industry collaboration and co-development across the entire ecosystem to ensure interoperability between components, hardware, architectures, connectivity, mechanical integrity, and signal integrity, addressing the physical challenges of electrical channels and designing high-performance mechanical solutions.

Designing or redesigning 224 Gbps solutions necessitates seamless electrical connectivity between all components to prevent performance bottlenecks that could impact the overall system. Adopting a co-development mindset from the initial concept phase is crucial for creating a transparent approach to identifying and addressing signal integrity and other performance risks.

High-Speed Board-to-Board Connectivity Enhances AI Applications

By enabling rapid data exchange between GPUs, accelerators, and other components, high-speed board-to-board connectors significantly enhance the efficiency of AI applications. Equally important, integrating these connectors ensures uninterrupted communication between processors, memory modules, and other critical components. In addition to meeting 224 Gbps-PAM4 requirements, all components and interconnect devices must also be robust enough to withstand environmental stresses such as vibration, temperature fluctuations, shock, and physical handling.

Supporting high data transfer rates helps achieve the performance levels required for complex computational and data processing tasks. Furthermore, the high data transfer rate capabilities of connectors are particularly beneficial for training and inference tasks, where timely data processing is critical to the performance of AI algorithms.

Beyond speed and efficiency, the reliability of connectors and the integrity of the signals they transmit are also crucial. High-speed board-to-board connectors must be designed with a focus on signal integrity to ensure that transmitted data is accurate and distortion-free. This reliability is vital in applications where data accuracy is non-negotiable, such as in medical devices and aerospace systems.

These connectors also offer another advantage: supporting different stacking heights, providing engineers with greater design flexibility to select the most suitable product configurations for specific AI application needs, especially in space-constrained environments. For example, by mixing and matching 2.5mm and 5.5mm connectors, engineers can fine-tune the stacking height of connectors to achieve optimal performance and efficiency. Dense connector configurations also save valuable space on printed circuit boards (PCBs).

Mirror Mezz Enhanced Improves Signal Integrity and Modularity

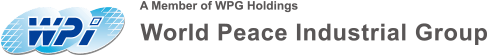

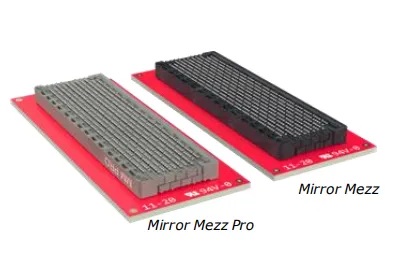

The latest addition to Molex's high-speed mezzanine connector series, Mirror Mezz Enhanced, supports 224 Gbps-PAM4. This advanced connector improves impedance tolerance and reduces crosstalk. Additionally, Molex offers different stacking heights using 2.5mm and 5.5mm connectors, maintaining industry-leading installation density.

The Mirror Mezz series connectors feature a highly scalable hermaphroditic design, allowing for easy cross-mating and offering ultra-low and medium stacking height options, including 5mm, 8mm, and 11mm configurations. This reduces mating errors, simplifies assembly processes, and enhances usability, efficiency, and productivity while providing engineers with greater design freedom to choose configurations that best meet specific engineering requirements. This is particularly advantageous for space-constrained and complex design applications.

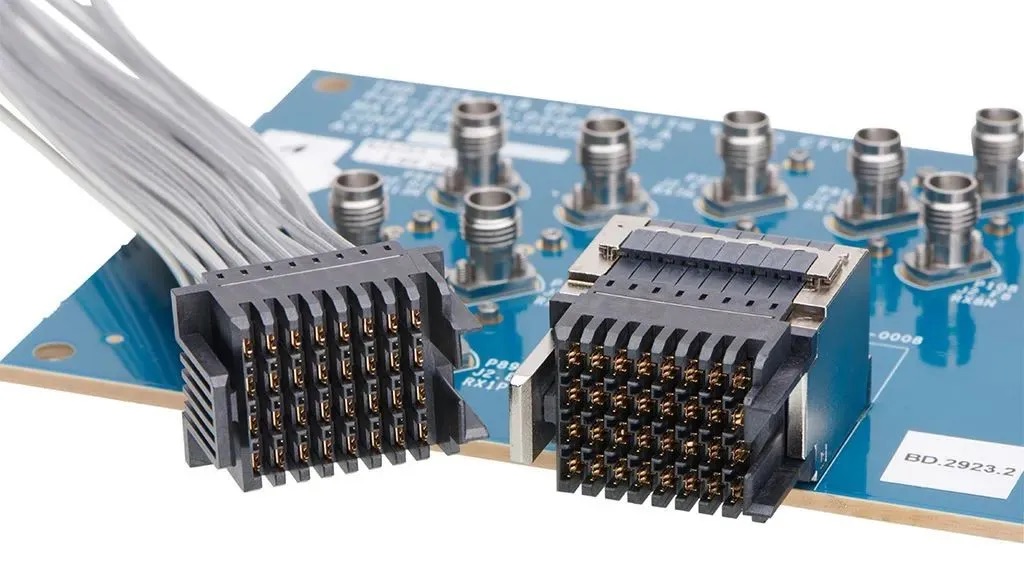

▲Mirror Mezz Board-to-Board Interconnect System

With Mirror Mezz, design engineers can combine two connectors to create three different configurations within the same design space. In contrast, traditional connector designs would require a total of six connectors, leading to increased material, tooling, manufacturing, and assembly costs. Mirror Mezz Enhanced also simplifies supply chain and Bill of Materials (BOM) management by reducing the number of part numbers.

Another major advantage of Mirror Mezz Enhanced is its ability to support 224 Gbps data transfer rates without compromising the configuration density of previous Mirror Mezz models. To ensure reliable performance at higher speeds, Molex optimized the terminal structure with a staggered pin layout and upgraded the manufacturing process to insert molding, achieving the precise layout and tolerances required for higher performance.

▲Mirror Mezz Pro & Mirror Mezz

Innovations in Connectivity for the 224G Ecosystem

Mirror Mezz Enhanced joins Molex's end-to-end 224G innovative solution portfolio. In May 2023, the company launched the industry's first chip-to-chip product lineup, which includes Mirror Mezz Enhanced, the Inception Cable Backplane System, CX2 Dual Speed near-ASIC connector-to-cable system, OSFP 1600 I/O solutions, as well as QSFP 800 and QSFP-DD 1600 I/O solutions.

1 Inception Cable Backplane System

The Inception Cable Backplane System is designed with a cable-first approach, supporting variable pitch density, optimal signal integrity, and easy integration with various system architectures, offering greater application flexibility.

▲Inception Backplane System

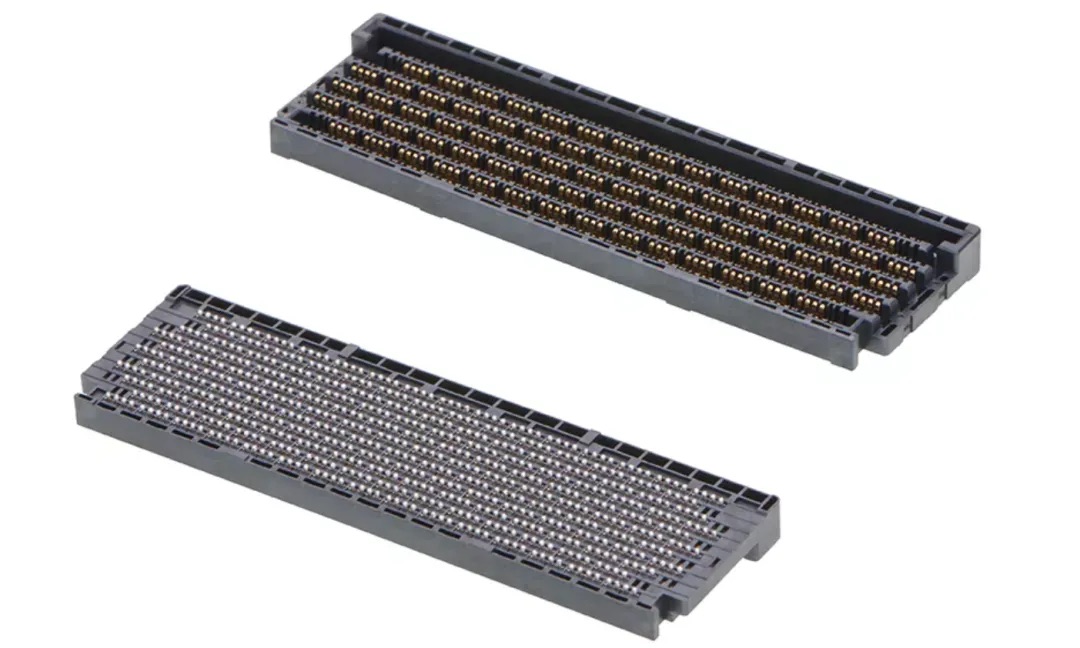

2 CX2 Dual Speed

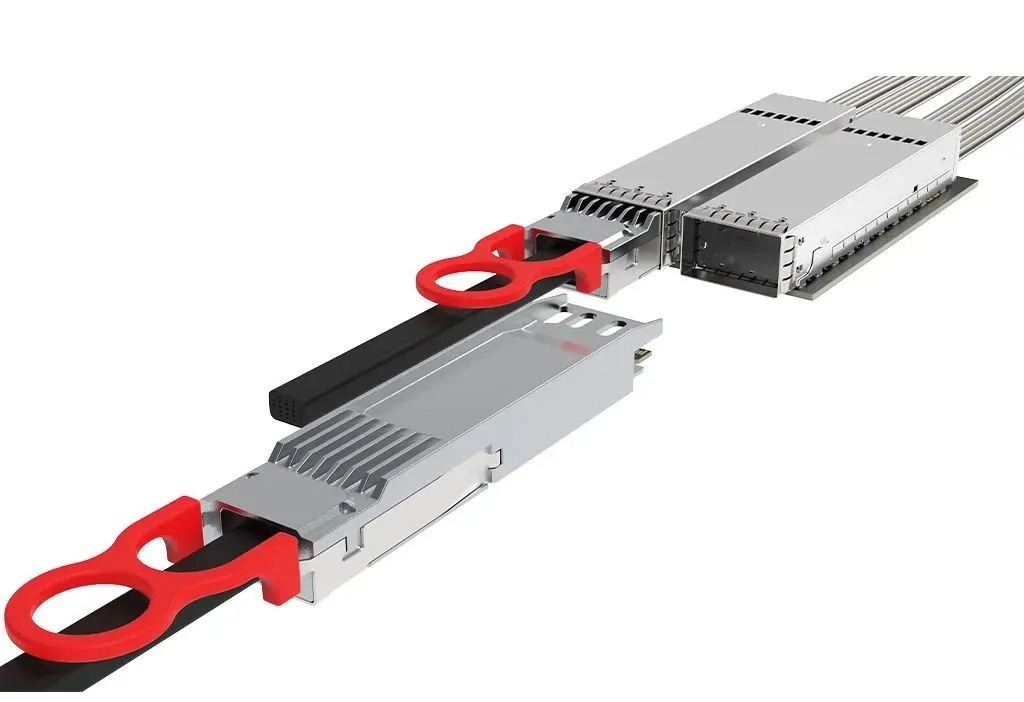

CX2 Dual Speed is Molex's 224 Gbps-PAM4 near-ASIC connector-to-cable system, offering post-mating screw engagement, integrated strain relief, reliable mechanical wiping, and fully protected "thumb-proof" mating interfaces to enhance long-term reliability.

▲CX2 Dual Speed Connection System

3 OSFP 1600 Solutions

The OSFP 1600 solutions further enhance the product portfolio, including SMT connectors and cages, BiPass, as well as Direct Attach Cables (DAC) and Active Electrical Cables (AEC) solutions, with each connector achieving per-channel 224 Gbps-PAM4 rates or a total rate of 1.6T.

▲OSFP 1600 Solutions

4 QSFP 800 and QSFP-DD Solutions

Like the OSFP product series, the QSFP 800 and QSFP-DD solutions offer upgraded features for SMT connectors and cages, BiPass, as well as DAC and AEC solutions, achieving per-channel 224 Gbps-PAM4 rates or a total rate of 1.5T per connector.

▲QSFP 800 Solutions

Embracing the Future of Next-Generation High-Speed Interconnects